**Service Manual**

# Tektronix

HFS 9009 Stimulus System

070-8366-03

Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service. Copyright © Tektronix, Inc. 1991, 1994. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### WARRANTY

Tektronix warrants that this product will be free from defects in materials and workmanship for a period of one (1) year from the date of shipment. If any such product proves defective during this warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for packaging and shipping the defective product to the service center designated by Tektronix, with shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the Tektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate maintenance and care. Tektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting from attempts by personnel other than Tektronix representatives to install, repair or service the product; b) to repair damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been modified or integrated with other products when the effect of such modification or integration increases the time or difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

|                              | General Safety Summary                                                                                                                                                                                                                                                                                                                                                                                                                                               | vii                                                                                                                       |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                              | Service Safety Summary                                                                                                                                                                                                                                                                                                                                                                                                                                               | xi                                                                                                                        |

| Specifications               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |

|                              | Nominal Traits                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>1–1</b><br>1–8<br>1–11                                                                                                 |

| <b>Operating Information</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |

|                              | Menu Selections                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>2–1</b><br>2–2<br>2–2<br>2–4<br>2–4                                                                                    |

| Theory of Operation          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                           |

| Performance Verificati       | Module Descriptions         Mainframe         Backplane         Power Supply         Fans         Front Panel         Cards         CPU Card         Time Base Card         Pulse Generator Cards         Data Time Generator Cards                                                                                                                                                                                                                                  | <b>3–1</b><br>3–1<br>3–1<br>3–1<br>3–1<br>3–1<br>3–2<br>3–2<br>3–2<br>3–2<br>3–3                                          |

|                              | Required Test EquipmentTest RecordVerification SequenceSelf TestCalibrationCheck ProceduresInstrument SetupOutput Level Checks (HFS 9DG1 Card Only)Output Level Checks (HFS 9DG2 and HFS 9PG2 Cards Only)Output Level Checks (HFS 9PG1 Card Only)Trigger Output LevelRise Time and Fall Time Checks (HFS 9PG1 and HFS 9DG1 Cards Only)Rise Time and Fall Time Checks (HFS 9PG2 and HFS 9DG2 Cards Only)Edge Placement ChecksFrequency Accuracy CheckPhase Lock Check | <b>4–1</b><br>4–2<br>4–11<br>4–12<br>4–13<br>4–13<br>4–13<br>4–16<br>4–19<br>4–21<br>4–22<br>4–25<br>4–27<br>4–31<br>4–34 |

Maintenance

## **Adjustment Procedures**

| Preventive Maintenance                 |

|----------------------------------------|

| Removal and Replacement                |

| Front Panel                            |

| Front Panel Keypad and Encoder Switch  |

| Display Module                         |

| Top Panel Circuit Board and Trim Bezel |

| ON/STANDBY Switch                      |

| Cards                                  |

| Mainframe Top Cover                    |

| Power Supply (lower back panel)        |

| Fans (upper back panel)                |

| Fan (side panel)                       |

| Troubleshooting                        |

| Power-On Diagnostics                   |

| Kernel-Test Diagnostics                |

| Controller-Test Diagnostics            |

| Self-Test Diagnostics                  |

| Self-Test Diagnostics                  |

| Calibration                            |

| Error Indications                      |

| Bit Assignments For Diagnostic LEDs    |

| Diagnostic Procedure                   |

### Options Electrical Parts List Diagrams

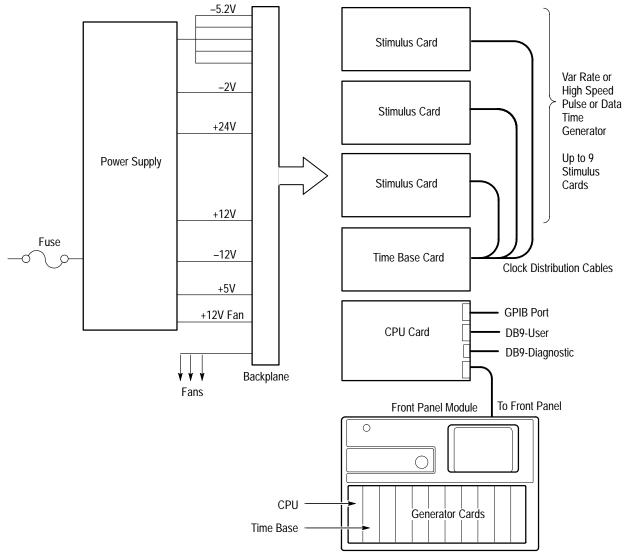

|                       | Block Diagram | 9–1 |

|-----------------------|---------------|-----|

| Mechanical Parts List |               |     |

| Replaceable Parts List           | 10-1 |

|----------------------------------|------|

| Parts Ordering Information       | 10-1 |

| Using the Replaceable Parts List | 10-2 |

# List of Figures

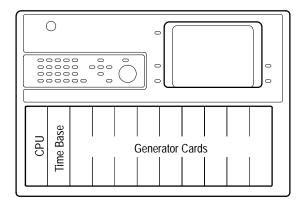

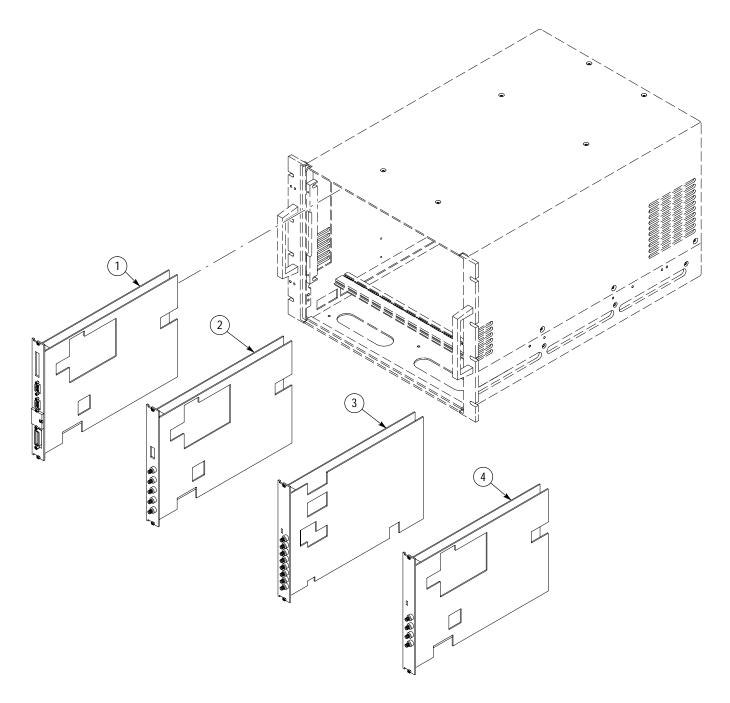

| Figure 2–1: HFS 9009 Mainframe, Cards, and Front Panel                                              | 2–1   |

|-----------------------------------------------------------------------------------------------------|-------|

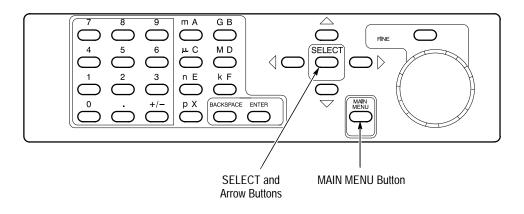

| Figure 2–2: MAIN MENU, SELECT, and Arrow Button Locations .                                         | 2–2   |

| Figure 2–3: Main Menu Display                                                                       | 2–2   |

| Figure 2–4: The Time Base Menu                                                                      | 2–3   |

| Figure 2–5: Mode set to Auto-Burst                                                                  | 2–3   |

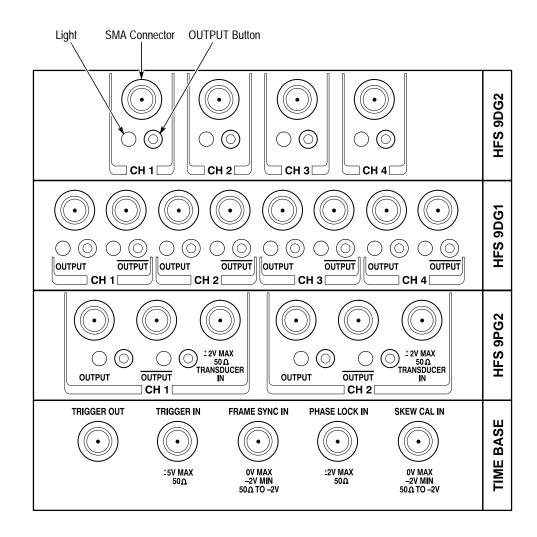

| Figure 2–6: Controls and Connectors for the Pulse Generator, Data<br>Generator, and Time Base Cards | 2–5   |

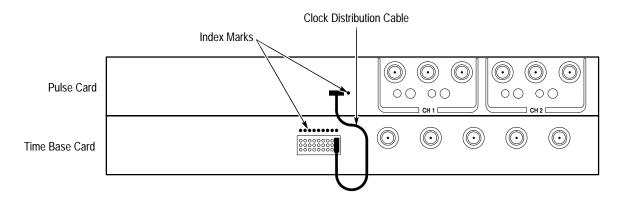

| Figure 6–1: Clock Distribution Cable Location                                                       | 6–6   |

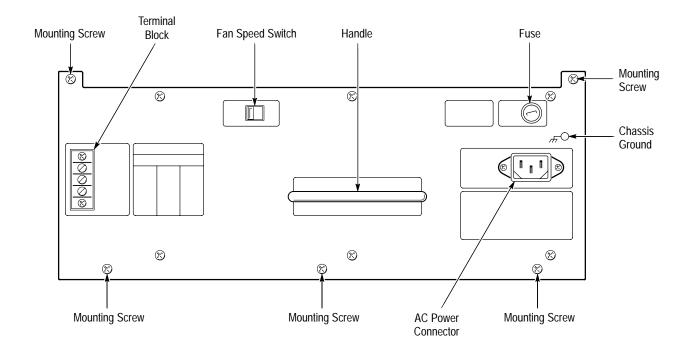

| Figure 6–2: HFS 9009 Power Supply (rear view)                                                       | 6-8   |

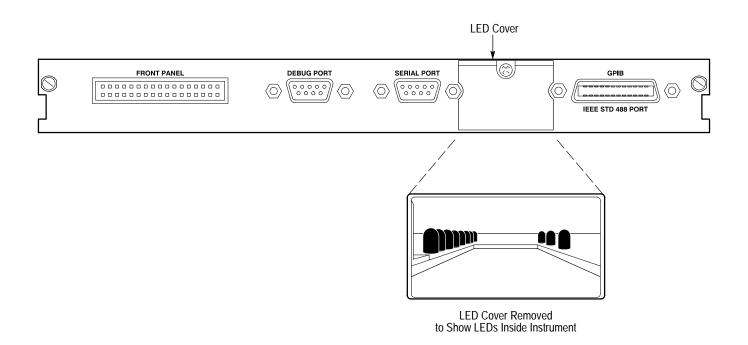

| Figure 6–3: The Location of LEDs on the CPU Card                                                    | 6–14  |

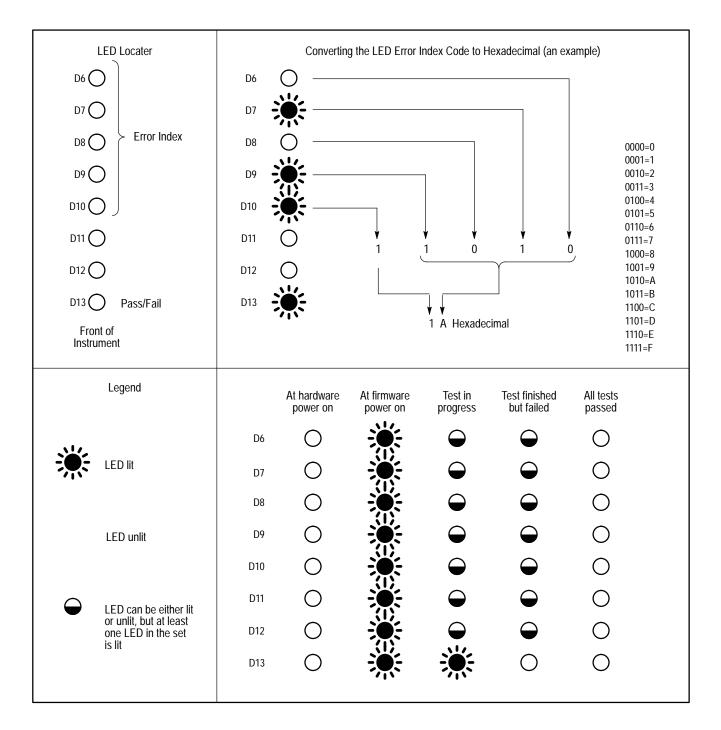

| Figure 6–4: Bit Assignments for Diagnostic LEDs                                                     | 6–15  |

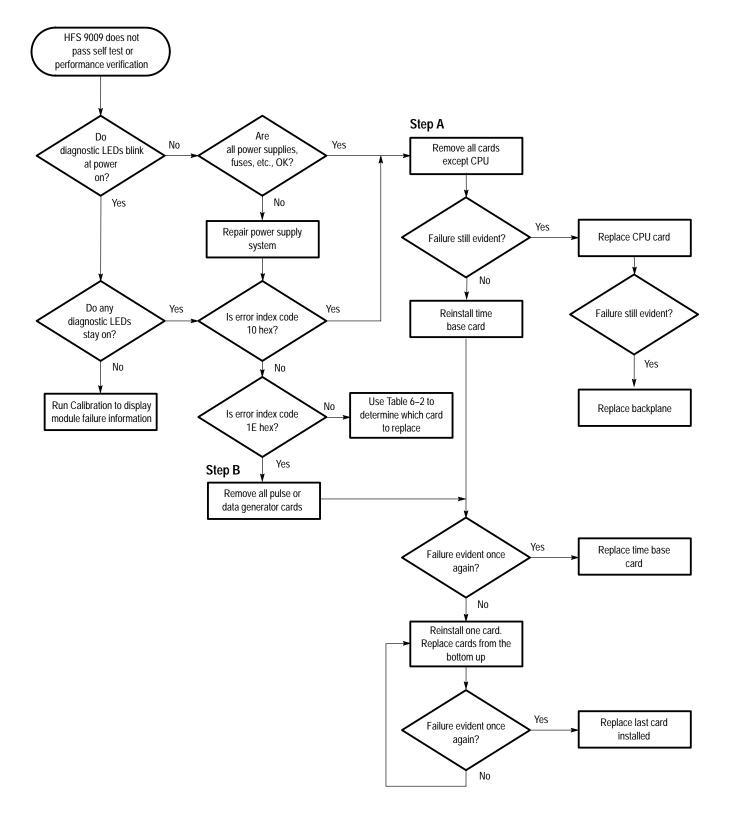

| Figure 6–5: Diagnostic Procedure Flowchart                                                          | 6–17  |

| Figure 9–1: Module Block and Interconnection Diagram                                                | 9–2   |

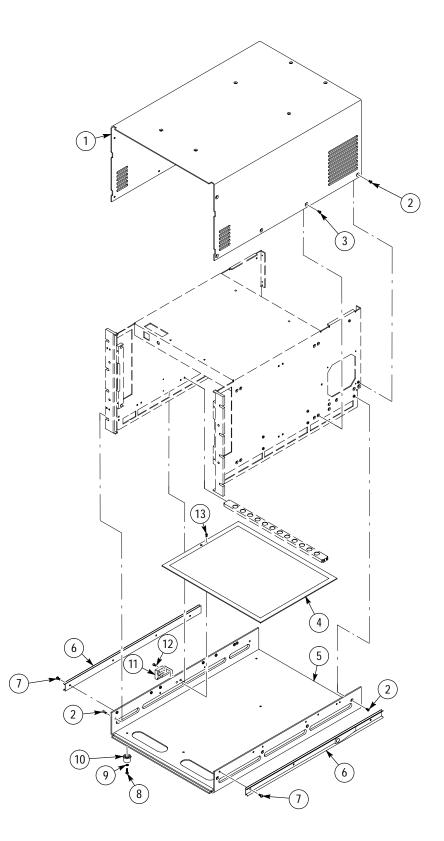

| Figure 10–1: Cabinet                                                                                | 10–5  |

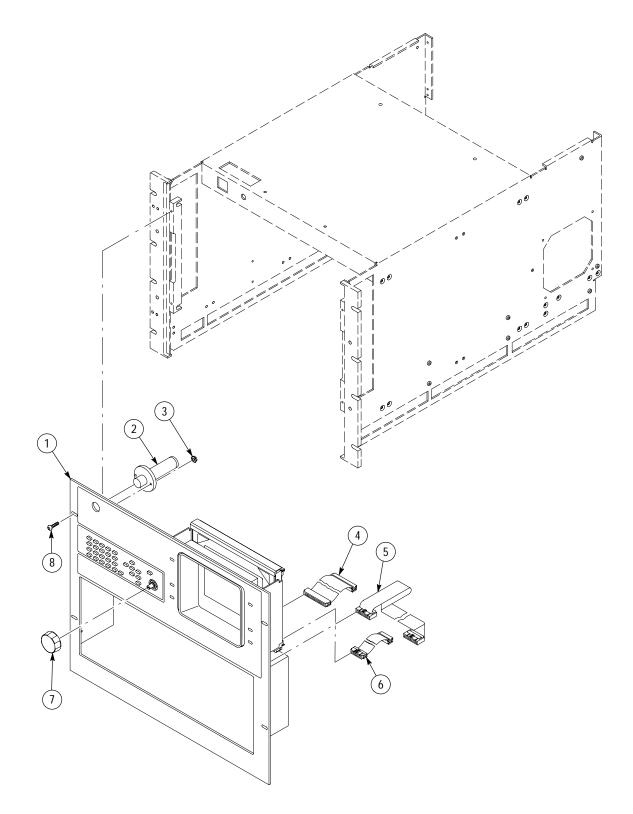

| Figure 10–2: Front Panel                                                                            | 10–7  |

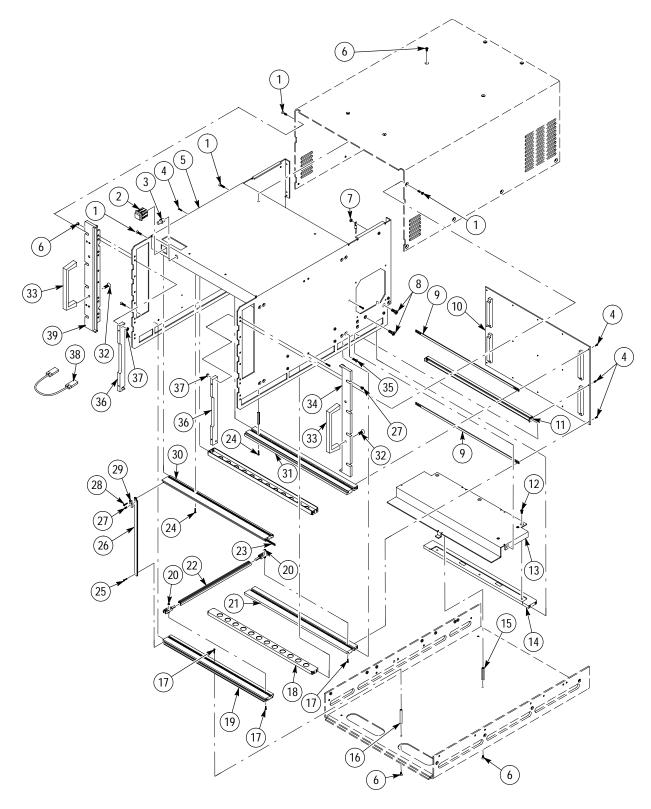

| Figure 10–3: Mainframe and Chassis Parts                                                            | 10-9  |

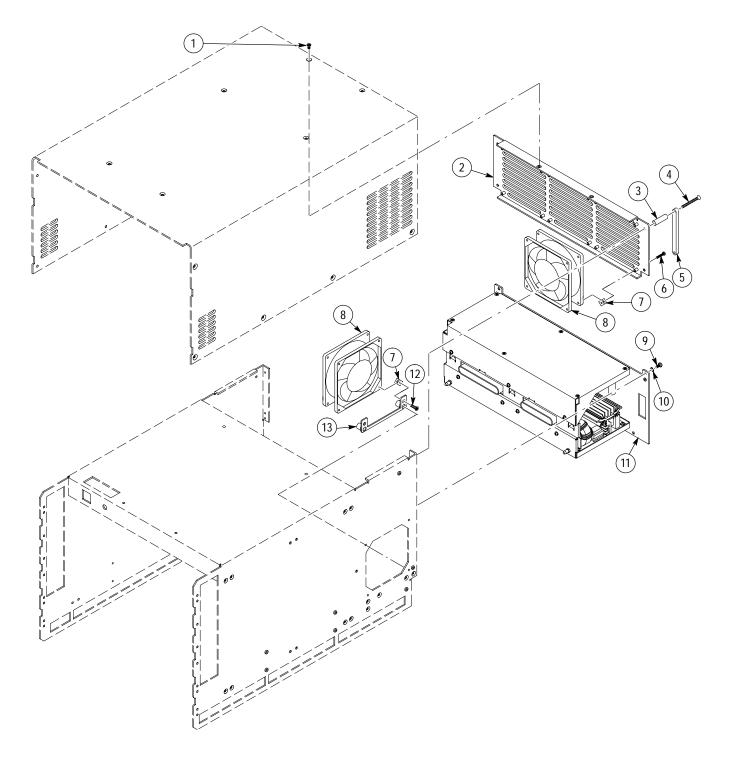

| Figure 10-4: Power Supply and Fan Assembly                                                          | 10-11 |

| Figure 10–5: Circuit Cards                                                                          | 10-13 |

|                                                                                                     |       |

# **List of Tables**

| Table 1–1: Nominal Traits — HFS 9PG1 Output Performance                                                                   | 1–1  |

|---------------------------------------------------------------------------------------------------------------------------|------|

| Table 1–2: Nominal Traits — HFS 9PG2 Output Performance                                                                   | 1–2  |

| Table 1–3: Nominal Traits — HFS 9DG1 Output Performance                                                                   | 1–3  |

| Table 1–4: Nominal Traits — HFS 9DG2 Output Performance                                                                   | 1–3  |

| Table 1–5: Nominal Traits — Time Base                                                                                     | 1–4  |

| Table 1–6: Nominal Traits — Performance to External Frequency                                                             |      |

| Reference                                                                                                                 | 1–4  |

| Table 1–7: Nominal Traits — Output Edge Placement Performance                                                             | 1–5  |

| Table 1–8: Nominal Traits — Transducer In Performance                                                                     | 1–5  |

| Table 1–9: Nominal Traits — Skew Cal In Performance                                                                       | 1–5  |

| Table 1–10: Nominal Traits — Trigger In Performance                                                                       | 1–6  |

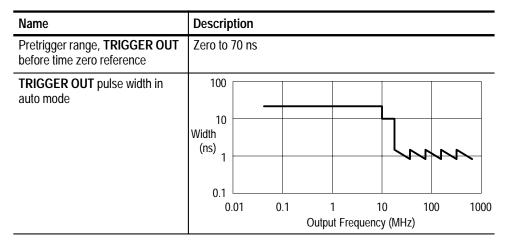

| Table 1–11: Nominal Traits — Trigger Out Performance                                                                      | 1–6  |

| Table 1–12: Nominal Traits — Power Requirements                                                                           | 1-6  |

| Table 1–13: Nominal Traits — System Memory Performance                                                                    | 1-6  |

| Table 1–14: Nominal Traits — HFS 9003 Mechanical                                                                          | 1–7  |

| Table 1–15: Nominal Traits — HFS 9009 Mechanical                                                                          | 1–7  |

| Table 1–16: Warranted Characteristics — HFS 9PG1 Output                                                                   |      |

| Performance                                                                                                               | 1–8  |

| Table 1–17: Warranted Characteristics — HFS 9PG2 Output                                                                   |      |

| Performance                                                                                                               | 1–8  |

| Table 1–18: Warranted Characteristics — HFS 9DG1 Output         Defense                                                   | 1 0  |

| Performance                                                                                                               | 1–8  |

| Table 1–19: Warranted Characteristics — HFS 9DG2 Output         Performance                                               | 1–9  |

| Table 1–20: Warranted Characteristics — Time Base                                                                         | 1-9  |

| Table 1–20: Warranted Characteristics — Third Dasc         Table 1–21: Warranted Characteristic — Performance to External | 1-7  |

| Frequency Reference                                                                                                       | 1–9  |

| Table 1–22: Warranted Characteristics — Output Edge Placement                                                             |      |

| Performance                                                                                                               | 1–9  |

| Table 1–23: Warranted Characteristics — Trigger Out Performance                                                           | 1–10 |

| Table 1–24: Warranted Characteristics — Power Requirements                                                                | 1–10 |

| Table 1–25: Warranted Characteristics — Environmental and                                                                 |      |

| Safety                                                                                                                    | 1–10 |

| Table 1–26: Typical Characteristics — Time Base                                                                           | 1–11 |

| Table 1–27: Typical Characteristics — HFS 9PG1 Output                                                                     |      |

| Performance                                                                                                               | 1–11 |

| Table 1–28: Typical Characteristics — HFS 9PG2 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1–12  |

| Table 1–29: Typical Characteristics — HFS 9DG1 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1–12  |

| Table 1–30: Typical Characteristics — HFS 9DG2 Output         Partnerse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 1 2 |

| Performance<br>Table 1–31: Typical Characteristics — Performance to External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–12  |

| Frequency Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1–13  |

| Table 1–32: Typical Characteristics — Transducer In Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1–13  |

| Table 1–33: Typical Characteristics — Trigger In Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–13  |

| Table 1–34: Typical Characteristics — Trigger Out Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1–14  |

| Table 1–35: Typical Characteristics — Power Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1–14  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| Table 4–1: Required Test Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4–1   |

| Table 4–2: Trigger Output Level and Phase Lock Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4–3   |

| Table 4–3: Test Record for HFS 9DG1 Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–4   |

| Table 4–4: Test Record for HFS 9DG2 Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–6   |

| Table 4–5: Test Record for HFS 9PG1 Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–7   |

| Table 4–6: Test Record for HFS 9PG2 Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–9   |

| Table 4–7: HFS 9DG1 Output Level Checks, First Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4–14  |

| Table 4–8: HFS 9DG1 Output Level Checks, Second Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–14  |

| Table 4–9: HFS 9DG1 Output Level Checks, Third Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4–15  |

| Table 4–10: HFS 9DG1 Output Level Checks, Fourth Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4–15  |

| Table 4–11: HFS 9DG2 and HFS 9PG2 Output Level Checks, First                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–17  |

| Table 4–12: HFS 9DG2 and HFS 9PG2 Output Level Checks, Second         Securities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4 18  |

| Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4–17  |

| Table 4–13: HFS 9PG2 Output Level Checks, Third Settings         The set of | 4–18  |

| Table 4–14: HFS 9PG2 Output Level Checks, Fourth Settings         The set of the set o | 4–18  |

| Table 4–15: HFS 9PG1 Output Level Checks, First Settings         Table 4–15: HFS 9PG1 Output Level Checks, First Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4–19  |

| Table 4–16: HFS 9PG1 Output Level Checks, Second Settings         The set of the set o | 4–20  |

| Table 4–17: HFS 9PG1 Output Level Checks, Third Settings         Table 4–10: HFS 9PG1 Output Level Checks, Third Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4–20  |

| Table 4–18: HFS 9PG1 Output Level Checks, Fourth Settings         The set of the set o | 4–21  |

| Table 4–19: Settings for Trigger Output Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4–22  |